|

|

ENCICLOPÉDIA DE RÁDIO ELETRÔNICA E ENGENHARIA ELÉTRICA Barramento de controle I2C. Enciclopédia de Rádio Eletrônica e Engenharia Elétrica

Enciclopédia de eletrônica de rádio e engenharia elétrica / informática I2C é uma interface de dois fios desenvolvida pela Philips. A especificação original da interface tinha uma taxa de dados máxima de 100 Kbps. No entanto, ao longo do tempo, surgiram padrões para modos de operação mais rápidos.2C. Para um pneu I2C, dispositivos com diferentes taxas de acesso podem ser conectados, pois a taxa de dados é determinada pelo sinal de clock. O protocolo de transferência de dados é projetado de forma a garantir a recepção confiável dos dados transmitidos. Na transferência de dados, um dispositivo é o "Mestre", que inicia a transferência de dados e gera os sinais de sincronização. Outro dispositivo "Slave" - inicia a transmissão apenas sob comando do "Mestre". Nos microcontroladores PIC16CXXX, o modo “Slave” do dispositivo é implementado em hardware no módulo SSP. O modo "Mestre" é implementado no software. Termos básicos usados na descrição da operação do barramento I2C: Transmissor - um dispositivo que transmite dados em um barramento Receptor - um dispositivo que recebe dados do barramento "Mestre" - um dispositivo que inicia a transmissão e gera um sinal de relógio "escravo" - dispositivo acessado por "Mestre" Múltiplo "Mestre" - modo de ônibus I2C com mais de um "Mestre" Arbitragem - procedimento para garantir que apenas um "Master" controle o barramento sincronização - procedimento para sincronizar o sinal de clock de dois ou mais dispositivos Os estágios de saída dos condicionadores de relógio (SCL) e dados (SDA) devem ser feitos em circuitos de coletor aberto (drenagem) para combinar várias saídas e conectados ao positivo de potência através de um resistor externo para ter um nível "1" no o barramento quando nenhum dos dois dispositivos gera um sinal "0". A carga capacitiva máxima é limitada a 400pF. Inicialização e conclusão da transferência de dados Quando não há transferência de dados no barramento, os sinais SCL e SDA são altos devido a um resistor externo. Os sinais START e STOP são gerados pelo "Master" para determinar o início e o fim da transferência de dados, respectivamente. O sinal START é gerado por uma transição de alto para baixo do sinal SDA enquanto o sinal SCL é alto. O sinal STOP é definido como a transição SDA de baixo para alto quando o SCL está alto. Assim, durante a transmissão de dados, o sinal SDA só pode mudar quando o sinal SCL estiver baixo.

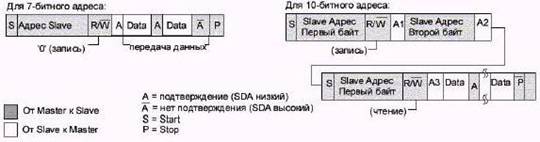

Endereçamento do dispositivo no barramento I2C Dois formatos de endereço são usados para endereçar dispositivos: Formato simples de 7 bits com bit de leitura/gravação R/W;

e formato de 10 bits - no primeiro byte, são transmitidos os dois bits mais significativos do endereço e o bit de escrita/leitura, no segundo byte, é transmitida a parte baixa do endereço.

Confirmação de aceitação Ao transmitir dados, após cada byte transmitido, o receptor deve confirmar o recebimento do byte com um sinal ACK. Se o "Slave" não acusar o recebimento do endereço ou byte de dados, o "Master" deve abortar a transmissão emitindo um sinal STOP. Ao transmitir dados do "Slave" para o "Master", o "Master" gera sinais de confirmação para receber dados ACK. Caso o “Master” não confirme o recebimento de um byte, o “Slave” para de transmitir os dados, “liberando” a linha SDA. O "Master" pode então gerar um sinal STOP. Para atraso na transferência de dados, o “Slave” pode definir um zero lógico, indicando que o “Master” deve aguardar. Após a "liberação" da linha SCL, a transmissão de dados continua.

Transferência de dados de "Mestre" para "Escravo"

Lendo dados de "Slave"

Usando o sinal re-START para acessar "Slave"

Modo multimestre Protocolo de comunicação I2C permite que você tenha mais de um "Mestre" no barramento. As funções de arbitragem e sincronização são usadas para resolver conflitos no barramento durante a inicialização da transferência. Arbitragem A arbitragem é executada na linha SDA quando a linha SCL está alta. Um dispositivo que conduz a linha SDA alta quando outro envia baixa perde o direito de levar "Mestre" e deve entrar no modo "Escravo". Um "mestre" que perdeu a iniciativa no barramento pode gerar pulsos de clock até o final do byte em que perdeu suas propriedades de mestre.

sincronização O clock no barramento ocorre após a arbitragem ter sido realizada no sinal SCL. Quando o sinal SCL vai de alto para baixo, todos os dispositivos interessados começam a contar a duração do nível baixo. Os dispositivos então começam a fazer a transição do SCL de baixo para alto de acordo com a taxa de dados necessária. Após a transição do nível de baixo para alto, os dispositivos interessados contam a duração do nível alto. O primeiro dispositivo a puxar o sinal SCL para baixo determina os parâmetros do relógio.

Publicação: cxem.net

Máquina para desbastar flores em jardins

02.05.2024 Microscópio infravermelho avançado

02.05.2024 Armadilha de ar para insetos

01.05.2024

▪ Novos ADCs multicanal programáveis de 16/14 bits ▪ Carregadores de carros elétricos em estacionamentos ▪ Internet de banda larga é um direito humano inalienável ▪ Transformando hidrogênio em metal

▪ seção do site Parâmetros de componentes de rádio. Seleção de artigos ▪ artigo de James Branch Cabell. Aforismos famosos ▪ artigo Trama. Dicas de viagem ▪ artigo Lenço voador. Segredo do Foco

Página principal | Biblioteca | Artigos | Mapa do Site | Revisões do site www.diagrama.com.ua |

Arabic

Arabic Bengali

Bengali Chinese

Chinese English

English French

French German

German Hebrew

Hebrew Hindi

Hindi Italian

Italian Japanese

Japanese Korean

Korean Malay

Malay Polish

Polish Portuguese

Portuguese Spanish

Spanish Turkish

Turkish Ukrainian

Ukrainian Vietnamese

Vietnamese

Deixe seu comentário neste artigo:

Deixe seu comentário neste artigo: